nuxt.js

面试题

软件定时器

笔记

安全测试

g++

业务大屏

IAR

信号量

visualstudio

网上书城

符号表导出

前端酒店管理系统

工企专利匹配

readelf

盒子模型

核酸预约检测管理系统

舌头

学生网页作业

Hotseat

DDR

2024/4/13 17:16:06Xilinx FPGA平台DDR3设计保姆式教程(3)MIG IP核使用教程及DDR读写时序

干货来了,用DDR搬砖,只需要会用IP就好,Xilinx官方YYDS! -----------------------------------------------------------------------------------------------------------------

汇总篇:

Xilinx平台DDR3设计保姆式教…

Xilinx FPGA平台DDR3设计保姆式教程(5)DDR3仿真篇

实验目的:

了解ddr的仿真模型建立。 汇总篇:

Xilinx FPGA平台DDR3设计保姆式教程(汇总篇)——看这一篇就够了 目录

一、Example Design

二、添加仿真文件 三、Testbench的编写 一、Example Design

每当我们例化了一个IP而不知…

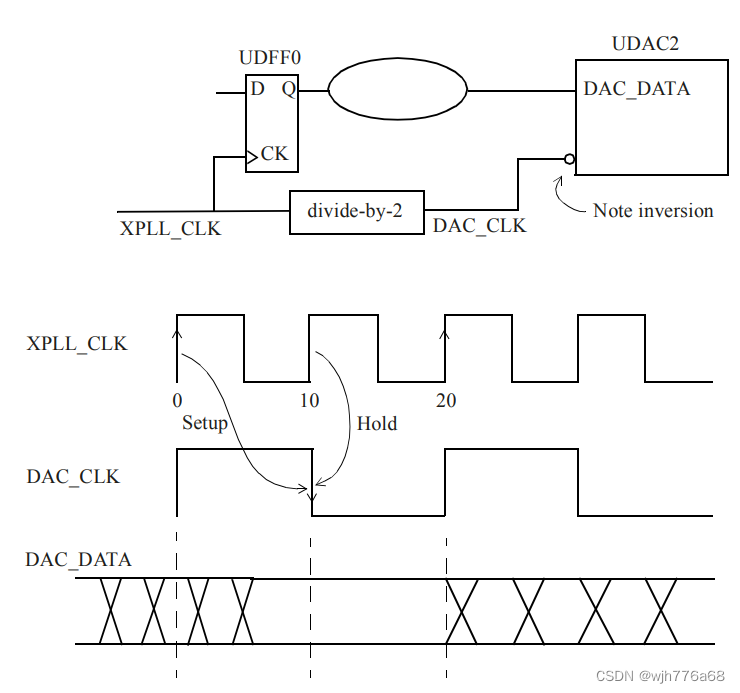

【STA】SRAM / DDR SDRAM 接口时序约束学习记录

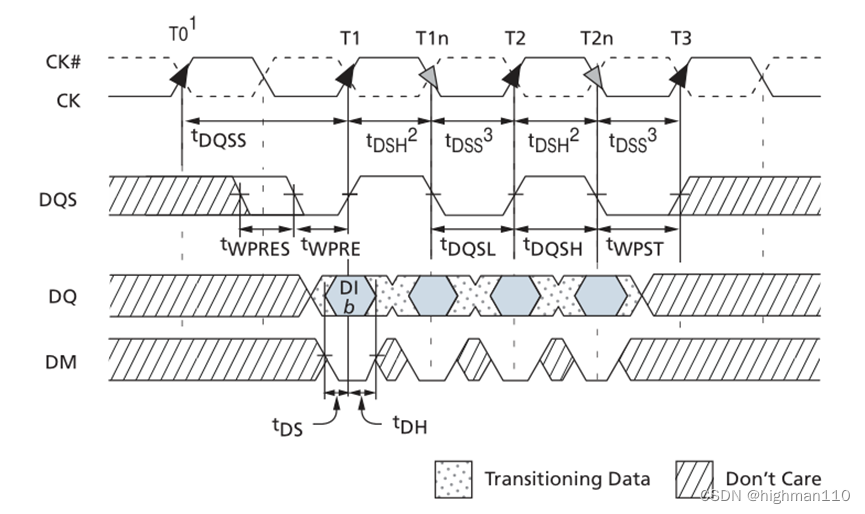

1. SRAM接口 相比于DDR SDRAM,SRAM接口数据与控制信号共享同一时钟。在用户逻辑(这里记作DUA(Design Under Analysis))将数据写到SRAM中去的写周期中,数据和地址从DUA传送到SRAM中,并都在有效时…

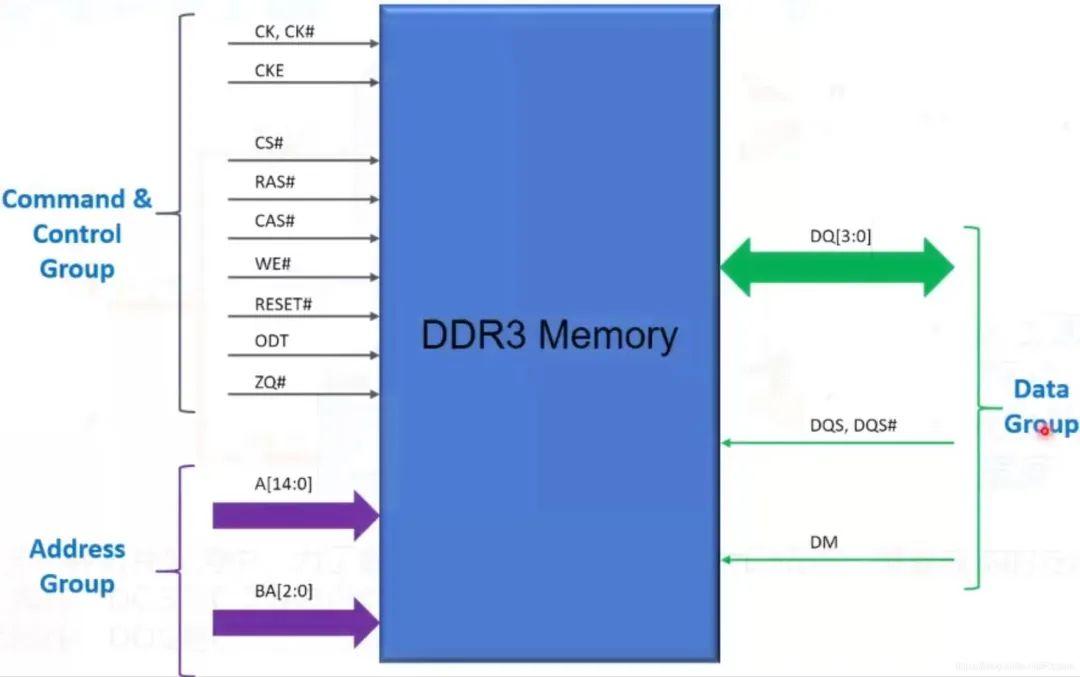

Xilinx FPGA平台DDR3设计保姆式教程(1)DDR3基础简介

如果我们只是拿来用ddr搬砖,那么它就简单,知道IP怎么使用就好,但是要想知其所以然,理论知识是必备的,这也是我们初学者所欠缺的东西,慢慢修炼吧! 汇总篇:

Xilinx平台DDR3设计保姆式…

Xilinx FPGA平台DDR3设计保姆式教程(汇总篇)——看这一篇就够了

DDR3设计,保姆式一站式教程,看这一篇文章就够了! 鉴于笔者最初接触DDR3时,被MIG那一堆信号搞得一脸懵逼,网上各种查资料的艰难回忆,决定借鉴大佬们的经验结合笔者自己的理解,整理一篇DDR3设计指…

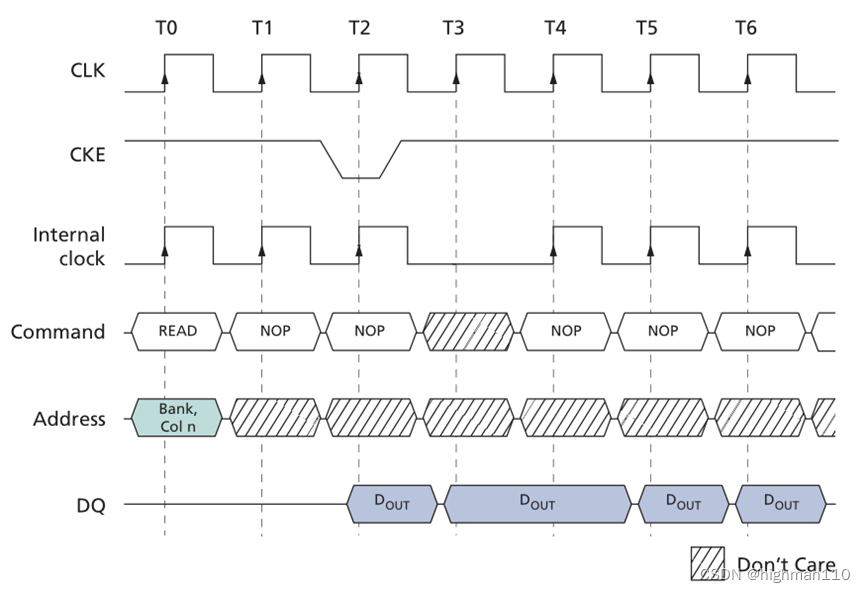

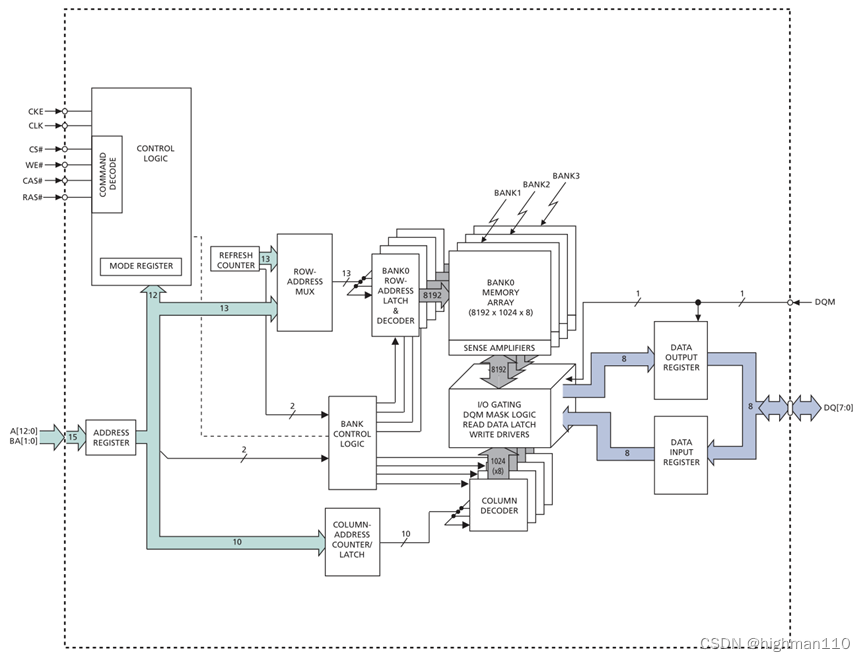

【DRAM存储器九】SDRAM介绍-read、write、Precharge、DQM、Power down、Clock Suspend命令

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光SDRAM数据手册》、《PC SDRAM specification》 目录…

【DDR】基于Verilog的DDR控制器的简单实现(一)——初始化

在FPGA中,大规模数据的存储常常会用到DDR。为了方便用户使用,Xilinx提供了DDR MIG IP核,用户能够通过AXI接口进行DDR的读写访问,然而MIG内部自动实现了许多环节,不利于用户深入理解DDR的底层逻辑。

本文以美光(Micro…

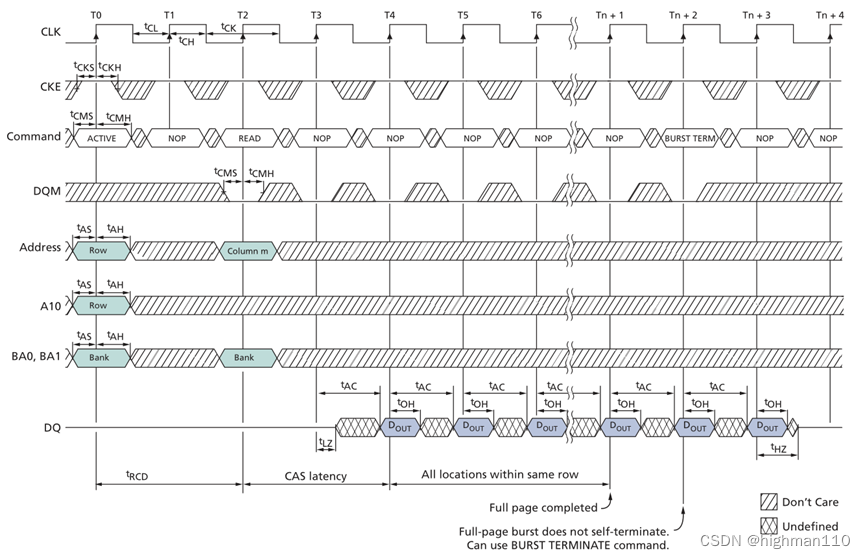

【DRAM存储器十一】SDRAM介绍-各类读操作详解,附带解释了几个重要时序参数

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光SDRAM数据手册》、《PC SDRAM specification》 目录

读…

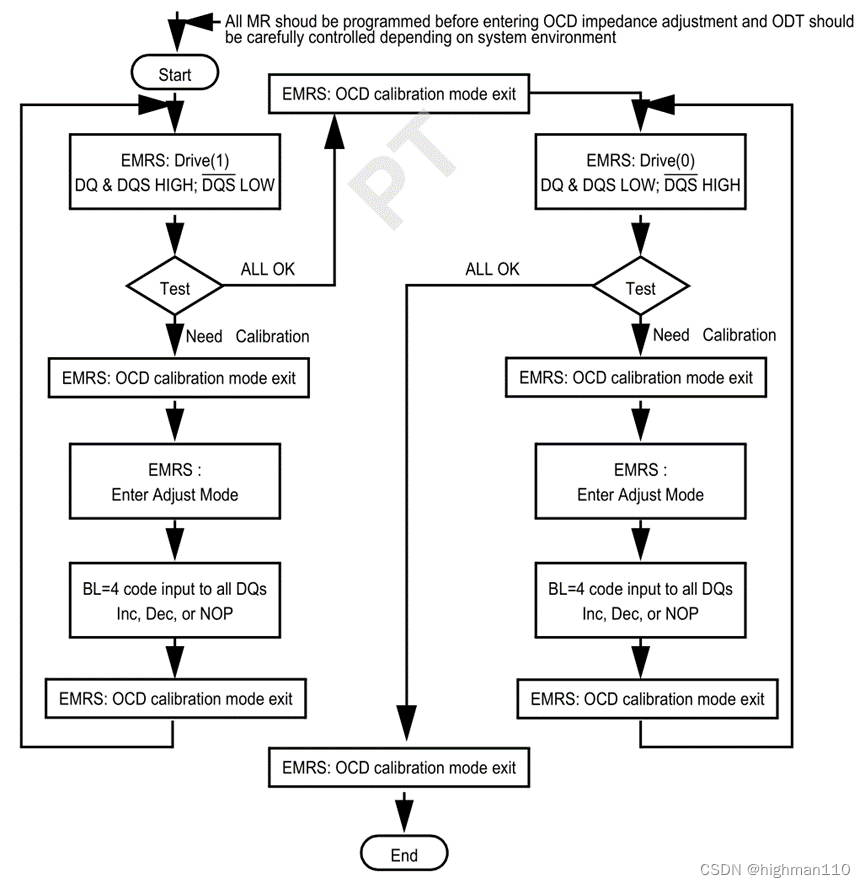

【DRAM存储器十七】DDR2介绍-DDR2的新增技术-Post CAS、ODT、RDQS、OCD

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光DDR数据手册》 目录

Post CAS

ODT

RDQS

OCD Post CA…

【DRAM存储器二十四】DDR4介绍-DDR4 MR0-3详解

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光DDR4数据手册》 、《JESD79-4B》

目录

MR0

MR1 MR2

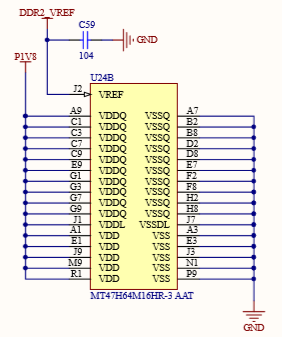

Xilinx FPGA平台DDR3设计详解(三):DDR3 介绍

本文介绍一下常用的存储芯片DDR3,包括DDR3的芯片型号识别、DDR3芯片命名、DDR3的基本结构等知识,为后续掌握FPGA DDR3的读写控制打下坚实基础。

一、DDR3芯片型号

电路板上的镁光DDR3芯片上没有具体的型号名。 如果想知道具体的DDR3芯片型号&#…

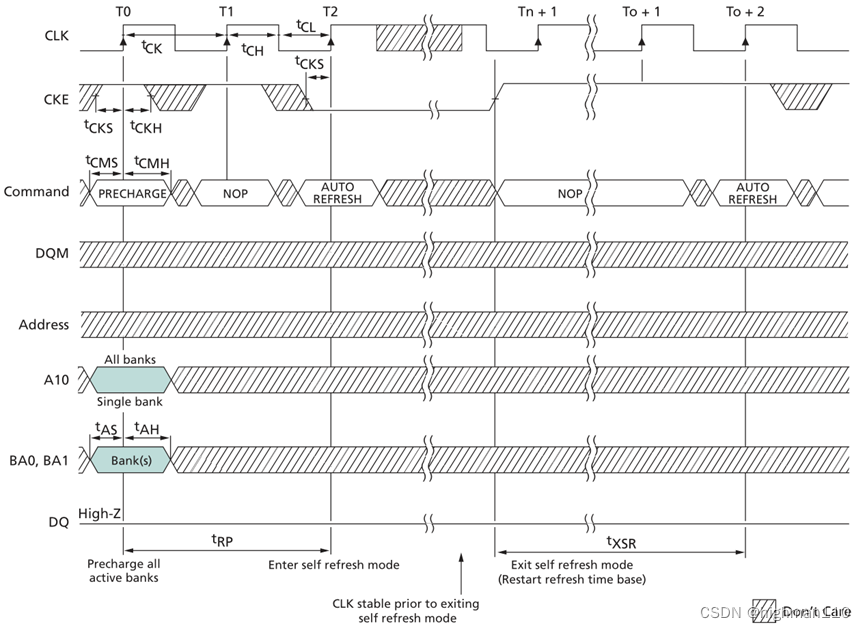

【DRAM存储器十】SDRAM介绍-刷新

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光SDRAM数据手册》、《PC SDRAM specification》 从前面的…

AG16KDDF256 User Manual

AGM AG16KDDF256 是由 AGM FPGA AG16K 与 DDR-SDRAM 叠封集成的芯片,具有 AG16K FPGA的可编程功能,提供更多可编程 IO,同时内部连接大容量 DDR-SDRAM。

FPGA 外部管脚 FBGA256 封装,管脚说明请见下表 Table-1: Tab…

内存DRAM,区分SDR和DDR

文章目录一、存储介质1.RAM:2.ROM:二、单说内存:1.问题:内存条是sram还是dram?2.内存:DRAM3.SDR和DDR内存条?4.How to区分SDR、DDRⅠ、DDRⅡ、DDRⅢ和DDRⅣ?1.看外观:2.看…

Xilinx FPGA平台DDR3设计保姆式教程(6)DDR高级篇

实验目的:

为了更方便的对DDR读写,我们对DDR再次封装成可复用的读写模块。 汇总篇:

Xilinx FPGA平台DDR3设计保姆式教程(汇总篇)——看这一篇就够了 目录

一、前言

二、方案设计

2.1 系统框图

2.2设计状态机 2.3…

Flash ddr调试

背景: Android T 流程:先确认所使用DDR类型(eMCP或分离式DDR+eMMC,可与项目经理确认),确认完DDR类型后,在官网online上面QVL查询是否有对应时序,若无,则可让flash供应商提供时序。 兼容基本路径如下: 此处以MT6580 2g版本为例: 1. \device\mediateksample\k80hd_re…

【DDR】DDR4学习记录

这里以美光DDR4芯片 MT40A512M16HA-075E datasheet 为例,说明DDR4存储器的原理及仿真。 根据开发板手册ug1302,在vcu128(xcvu37p)开发板上,共具有5块DDR4芯片,在数据信号上4块DDR4具有16位数据线&#…

Xilinx FPGA平台DDR3设计保姆式教程(4)DDR3读写测试

实验任务:

将输入数据(data_in)存入ddr,然后读出,验证输入输出数据是否相等。 汇总篇:

Xilinx FPGA平台DDR3设计保姆式教程(汇总篇)——看这一篇就够了 目录

一、前言

二、系统方案

2.1方案设计

2.1.…

【DRAM存储器七】SDRAM介绍-part1

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光SDRAM数据手册》、《PC SDRAM specification》 目录…

【DRAM存储器六】DRAM存储器的架构演进-part3

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考书籍:《Memory Systems - Cache, DRAM, Disk》 目录

以降低延时…

【DRAM存储器五】DRAM存储器的架构演进-part2

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考书籍:《Memory Systems - Cache, DRAM, Disk》 目录

LINUX-I.MX6U从零开始之1.10--DDR3

目录 文章目录目录一,啥是DDR31.1 RAM 随机存储器。1.2 ROM 只读存储器。1.3 SRAM 静态随机存储器。1.4 SDRAM 同步动态随机存储器。1.5 DDR->双倍速率 SDRAM二,购买DDR3,你要知道什么2.1 传输速率2.2 tRCD 参数2.3 CL参数2.4 AL参数2.5 t…

DDR电路的PCB布线规则

一、DDR电源:DDR一般需要3种电源,分别为:VDDQ、VREF、VTT。其中VTT和VREF的电平是一样的,为VDDQ电平的一半。VREF消耗的电流很小,可以通过分压电阻网络从VDDQ分压得到;而VTT是端接电源,电流会比…

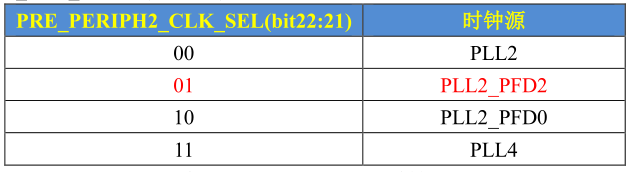

Xilinx FPGA平台DDR3设计保姆式教程(2)DDR3各时钟频率及带宽分析

对FPGA而言,时钟就是脉搏,必须理解透彻! 汇总篇:

Xilinx平台DDR3设计保姆式教程(汇总篇)——看这一篇就够了 时钟太重要了,单开一篇来说。 目录

一、如何知道器件所支持的时钟频率?…

【DRAM存储器十五】DDR介绍-关键技术之DLL和prefetch

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光DDR数据手册》 目录

DLL

预取

DDR SDRAM的几个新增时…

DDRC中的write exclusive

DDRC中的write exclusive为了在硬件层面支持读写互斥,就需要判断一个地址是否已被其他处理器或核心修改,在 ARM 处理器中包含了被称为 Exclusive Monitor 的状态机来维护内存的互斥状态,从而保证读写一致性。 状态机的起始状态为 Open&#x…

【带宽、主频、位宽、数据传输速率】DDR带宽怎么计算?

文章目录 1. 如何计算DDR带宽2. DDR data rate和DDR主频3. Mbps和Mhz4. 出题 1. 如何计算DDR带宽

计算DDR理论带宽的公式为:

DDR主频 * 位宽 理论带宽其中,位宽(bit width)指的是内存总线的位宽,例如64位、128位、16bit、32bit等ÿ…

【Verilog】基于Verilog的DDR控制器的简单实现(一)——初始化

在FPGA中,大规模数据的存储常常会用到DDR。为了方便用户使用,Xilinx提供了DDR MIG IP核,用户能够通过AXI接口进行DDR的读写访问,然而MIG内部自动实现了许多环节,不利于用户深入理解DDR的底层逻辑。

本文以美光(Micro…

嵌入式开发DDR的选择

摘要:

当前DDR主要有DDR、DDR2、DDR3、DDR4、DDR5等不同的内存标准。本文主要是对比不同标准的DDR,了解其差异性以及优劣势,以便在以后在以后做DDR选型的时候做一定的参考。

嵌入式设备常见的DDR内存标准

嵌入式常见的DDR内存标准有DDR、D…

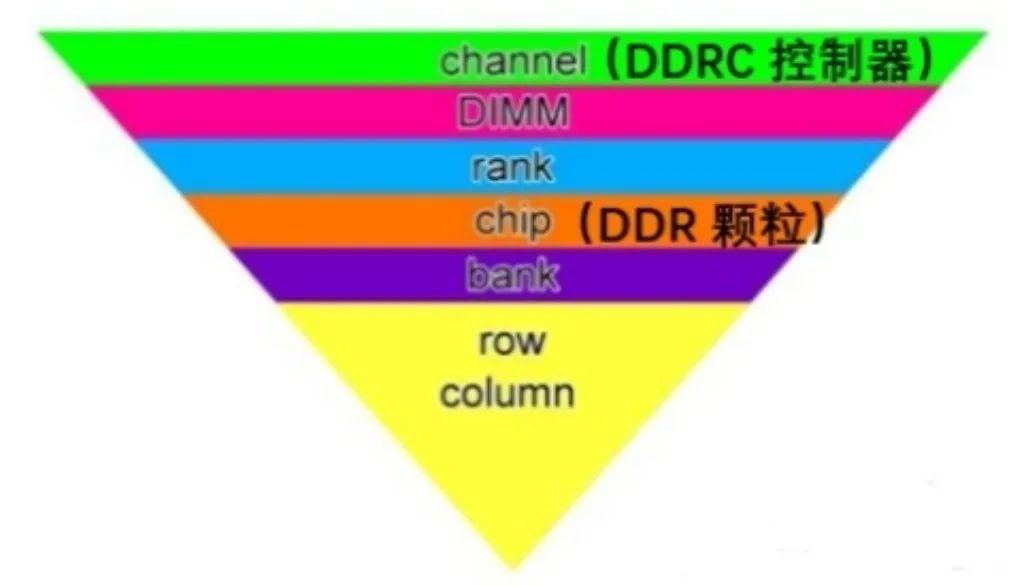

Xilinx FPGA平台DDR3设计详解(一):DDR SDRAM系统框架

DDR SDRAM(双倍速率同步动态随机存储器)是一种内存技术,它可以在时钟信号的上升沿和下降沿都传输数据,从而提高数据传输的速率。DDR SDRAM已经发展了多代,包括DDR、DDR2、DDR3、DDR4和DDR5,每一代都有不同的…